-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

- Floor Heating Systems & Parts

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

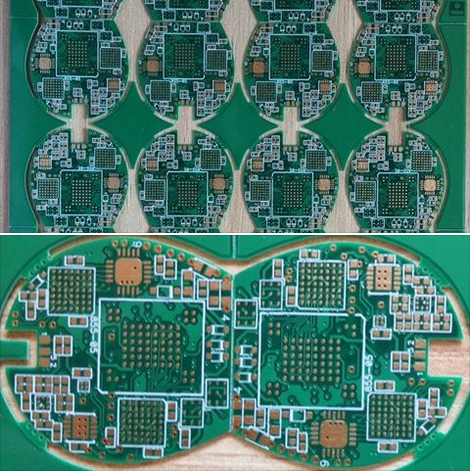

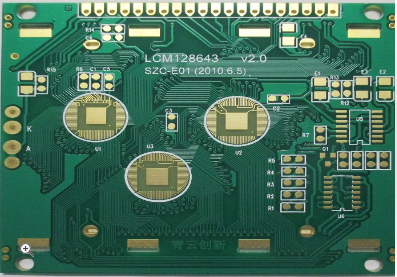

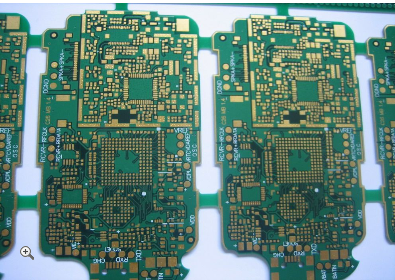

Robust Line Card PCB Layouts Ensuring Signal Integrity And Thermal Management

In the rapidly evolving landscape of networking and telecommunications, line cards serve as the backbone of modern communication systems, handling high-speed data transmission and processing. As data rates soar and component densities increase, the design of printed circuit boards (PCBs) for these line cards becomes increasingly critical. A robust PCB layout is not merely about connecting components; it is a delicate balancing act that ensures signal integrity and effective thermal management. Without these, systems can suffer from data corruption, reduced performance, or even premature failure due to overheating. This article delves into the essential strategies for designing line card PCBs that withstand the demands of high-frequency operation and thermal stress, providing a foundation for reliable and efficient network infrastructure.

Signal Integrity Fundamentals

Signal integrity (SI) is paramount in line card designs, where high-speed signals traverse the PCB at gigabit rates. At these frequencies, even minor imperfections in the layout can lead to reflections, crosstalk, and electromagnetic interference (EMI), degrading overall system performance. To mitigate these issues, designers must prioritize controlled impedance routing. This involves calculating and maintaining consistent trace widths and dielectric spacing to match the characteristic impedance of the transmission lines, typically 50 or 100 ohms for differential pairs. By doing so, signal reflections are minimized, ensuring clean data transmission from drivers to receivers.

Another critical aspect is managing signal return paths and minimizing crosstalk. High-speed signals require low-inductance return paths, which can be achieved through proper grounding schemes, such as using solid ground planes adjacent to signal layers. Additionally, spacing sensitive traces apart and employing guard traces or ground shields can reduce crosstalk between adjacent channels. For differential signaling common in high-speed interfaces like Ethernet or PCIe, maintaining tight pair coupling and equal trace lengths is essential to preserve signal timing and reject common-mode noise. Simulation tools play a vital role here, allowing designers to model signal behavior and optimize layouts before fabrication, thus preventing costly revisions.

Thermal Management Techniques

As line cards pack more functionality into smaller form factors, thermal management becomes a critical concern. Excessive heat can degrade component performance, reduce lifespan, and lead to thermal runaway. Effective heat dissipation starts with strategic component placement, where high-power devices like processors or ASICs are positioned to maximize airflow and minimize hotspots. Designers should also incorporate thermal vias—plated holes that transfer heat from components to internal ground planes or dedicated thermal layers, acting as conduits for heat flow away from sensitive areas.

Beyond layout, the selection of materials and auxiliary cooling methods is crucial. Using PCBs with higher thermal conductivity substrates, such as metal-core or insulated metal substrates, can enhance heat spreading. Forced air cooling via fans or heat sinks attached to high-power components further aids in maintaining safe operating temperatures. Thermal simulation software allows engineers to predict temperature distributions and identify potential issues early in the design phase. By integrating these techniques, designers can ensure that line cards operate reliably under heavy loads, preventing thermal-induced failures and extending product longevity.

Power Integrity and Distribution

Power integrity (PI) is closely intertwined with signal integrity and thermal management, as unstable power delivery can introduce noise and exacerbate heating. In line card PCBs, robust power distribution networks (PDNs) are essential to supply clean, stable voltage to all components. This begins with proper decoupling capacitor placement—positioning capacitors close to power pins of integrated circuits to suppress high-frequency noise and provide local charge storage. A multi-layer approach with dedicated power and ground planes helps reduce impedance and ensures low-inductance return paths for current flow.

Additionally, managing voltage regulator modules (VRMs) and their associated components is key to minimizing power losses and heat generation. Designers should use wide traces or polygons for power rails to handle high currents without excessive voltage drops. Simulations for power plane resonance and impedance profiling can identify potential issues like ground bounce or supply ripple. By optimizing the PDN, designers not only enhance signal quality but also contribute to thermal stability, as efficient power delivery reduces wasteful energy conversion into heat, supporting overall system robustness.

EMI/EMC Considerations

Electromagnetic interference (EMI) and electromagnetic compatibility (EMC) are critical in line card designs, especially in densely populated systems where radiated emissions can disrupt adjacent circuitry or fail regulatory standards. To achieve EMI control, PCB layouts must incorporate shielding and careful routing practices. This includes using ground planes to contain electromagnetic fields, avoiding sharp bends in high-speed traces that can act as antennas, and implementing split power planes for analog and digital sections to prevent noise coupling.

Furthermore, filtering components such as ferrite beads or common-mode chokes can be integrated into signal and power lines to suppress high-frequency noise. Enclosure design and board stacking also play roles; for instance, placing high-speed layers between ground layers in the PCB stack-up can reduce radiation. Pre-compliance testing during the design phase helps identify EMI hotspots early, allowing for adjustments before final production. By addressing EMI/EMC proactively, designers ensure that line cards operate harmoniously in their intended environments, avoiding interference-related failures and ensuring compliance with international standards.

Design for Manufacturing and Testing

A robust line card PCB layout must not only perform well electrically and thermally but also be manufacturable and testable. Design for manufacturing (DFM) principles involve adhering to fabrication tolerances, such as minimum trace widths and clearances, to prevent issues like solder bridging or open circuits. Collaborating with PCB manufacturers early in the design process can help select appropriate materials and processes, such as controlled impedance testing or thermal reliability checks, to ensure consistency in mass production.

Similarly, design for testing (DFT) incorporates features like test points, boundary scan (JTAG) interfaces, and built-in self-test (BIST) capabilities to facilitate debugging and validation. These elements allow for efficient post-assembly testing, reducing time-to-market and costs associated with rework. By integrating DFM and DFT considerations, designers create line cards that are not only high-performing but also reliable and scalable in real-world applications, bridging the gap between theoretical design and practical deployment.

REPORT