-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

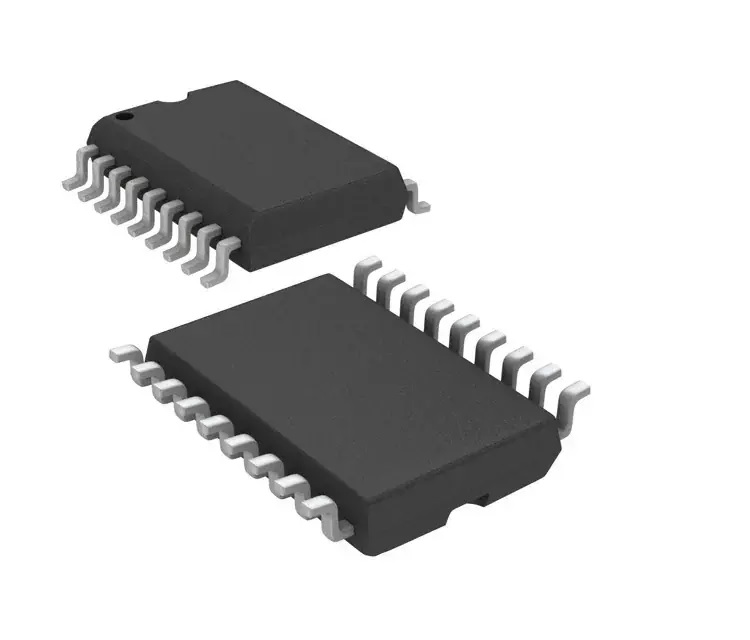

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

- Floor Heating Systems & Parts

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

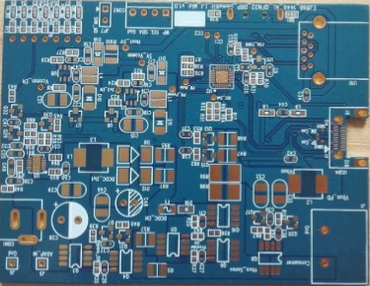

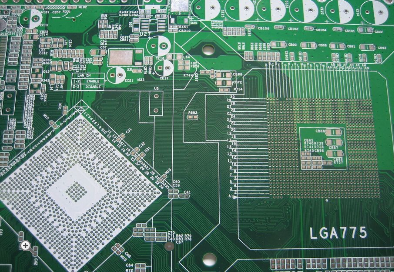

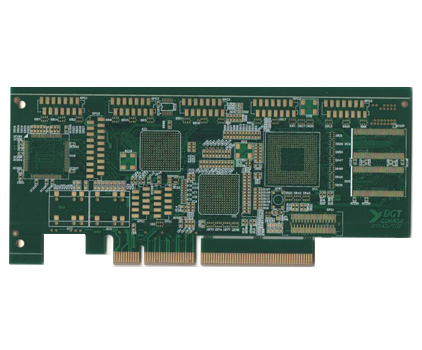

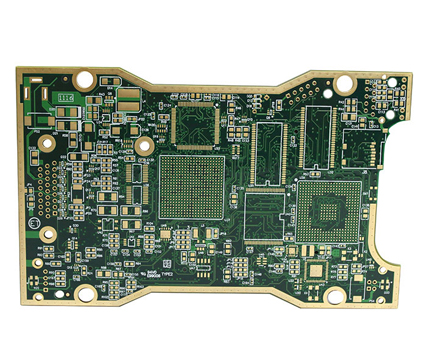

Impedance Control Challenges in High Frequency PCBs Solutions for Minimizing Crosstalk and Reflections in Demanding Applications

In the rapidly advancing landscape of modern electronics, the demand for higher data rates and faster signal processing has pushed operating frequencies into the gigahertz range and beyond. This evolution places unprecedented demands on printed circuit board (PCB) design, where the integrity of high-speed signals is paramount. At the heart of this challenge lies impedance control—the precise management of a trace's characteristic impedance to match the source and load impedances. Failures in this domain manifest as signal reflections, crosstalk, and electromagnetic interference (EMI), which can cripple the performance of critical applications such as 5G infrastructure, aerospace radar systems, high-performance computing, and advanced automotive radar. This article delves into the multifaceted challenges of achieving robust impedance control in high-frequency PCBs and explores comprehensive solutions to mitigate crosstalk and reflections, ensuring reliable operation in the most demanding environments.

Fundamental Impedance Control Challenges in High-Frequency Design

The primary goal of impedance control is to maintain a consistent characteristic impedance along a signal's entire path, typically targeting common values like 50Ω or 100Ω for differential pairs. At high frequencies, signals behave less like simple electrical connections and more like transmission lines, where the physical geometry of the PCB trace directly influences its electrical properties. The characteristic impedance (Z₀) is determined by the trace width, thickness, the dielectric constant (Dk) of the substrate material, and the height of the dielectric layer between the trace and its reference plane. A minor deviation in any of these parameters, often caused by manufacturing tolerances, can lead to a significant impedance mismatch.

This mismatch causes a portion of the signal to be reflected back toward the source whenever it encounters a discontinuity. These reflections result in signal distortion, overshoot, undershoot, and timing errors (jitter), which degrade the signal's quality and integrity. In time-domain reflectometry (TDR) analysis, these mismatches appear as impedance "bumps" or "dips" along the trace. Furthermore, as frequencies increase, the skin effect becomes more pronounced, forcing current to flow only on the surface of the conductor. This effectively reduces the cross-sectional area for current, increasing the trace's AC resistance and altering its impedance in a frequency-dependent manner, adding another layer of complexity to control efforts.

Material Selection and Stack-up Design for Controlled Impedance

The foundation of any high-frequency PCB is its material system and layer stack-up. Standard FR-4 epoxy laminates, while cost-effective, exhibit a dielectric constant that can vary with frequency and temperature, making precise impedance control difficult above a few gigahertz. For demanding applications, designers turn to advanced, low-loss laminate materials such as Rogers (RO4000 series), Isola (I-Tera), or Panasonic (Megtron). These materials offer a more stable and consistent Dk across a wide frequency range, lower dissipation factor (Df) to reduce signal attenuation, and better thermal management properties.

The stack-up design is equally critical. A symmetrical, tightly coupled stack-up with dedicated ground planes adjacent to signal layers is essential. This structure provides a clear, low-impedance return path for high-frequency currents, minimizing loop inductance and radiation. The precise calculation of dielectric thickness (H) is vital, as Z₀ is inversely proportional to it for a given trace width. Using field-solving tools integrated into PCB design software, engineers can model the cross-section of a trace to predict its impedance based on the chosen material's Dk and the proposed stack-up geometry before fabrication, allowing for preemptive adjustments.

Geometric Layout and Routing Strategies to Minimize Discontinuities

Even with perfect materials, poor layout practices can introduce impedance discontinuities. Key geometric factors include trace width, spacing, and the management of features like vias, bends, and pads. Trace width must be carefully calculated and maintained; narrowing a trace increases its inductance, raising impedance, while widening it increases capacitance, lowering impedance. Any change in width, even for a short segment to navigate a crowded area, creates a discontinuity.

Vias are particularly problematic as they represent a vertical transition between layers, introducing parasitic capacitance and inductance. To mitigate their impact, designers use techniques like back-drilling to remove unused via stubs, employ microvias in high-density interconnect (HDI) designs, and place ground return vias adjacent to signal vias to preserve the return path. For trace bends, 45-degree angles or curved arcs are preferred over 90-degree corners, which increase capacitance at the corner. Furthermore, maintaining consistent spacing between differential pairs and to other aggressive signals is crucial to control coupling.

Advanced Techniques for Suppressing Crosstalk

Crosstalk—the unwanted coupling of energy from one transmission line to another—becomes a dominant issue as edge rates accelerate and traces are packed more densely. It manifests as either capacitive (electric field) or inductive (magnetic field) coupling, leading to near-end crosstalk (NEXT) and far-end crosstalk (FEXT). The primary defense is increased spacing between traces, following the "3W rule" (spacing center-to-center equal to three times the trace width) or more aggressive rules for very sensitive signals.

When space is constrained, strategic use of grounded guard traces or via fences between aggressive signal lines can be highly effective. A guard trace, terminated to ground at both ends, acts as a shield that intercepts and sinks coupled energy. A via fence, a line of grounded vias placed along the side of a trace, helps contain electromagnetic fields, especially at the edges of a PCB or near connectors. Additionally, routing critical signals on different layers with an intervening ground plane as a shield provides excellent isolation. Careful management of layer assignments to avoid parallel routing of high-speed traces directly over or under each other for long distances is a fundamental best practice.

Mitigating Reflections Through Termination and Simulation

Reflections are managed by both minimizing discontinuities and implementing proper termination strategies. Termination provides a path for signal energy to be absorbed at the load, preventing it from reflecting back. For high-speed single-ended lines, series termination (a resistor placed near the driver) is often used, while parallel or AC termination (a resistor to ground, sometimes with a capacitor in series) may be used at the load end. For differential signals, differential termination is applied across the pair at the receiver.

However, theoretical calculations are insufficient. Pre-layout and post-layout simulation using specialized signal integrity (SI) tools is non-negotiable for demanding applications. Pre-layout simulation helps define impedance targets, stack-up, and routing rules. Post-layout simulation involves extracting the actual PCB geometry into a model to perform analyses like TDR to check for impedance variations, and eye diagram analysis to assess the signal's quality in the time domain under real-world conditions. These simulations allow engineers to identify problematic reflections, adjust trace lengths, fine-tune termination values, and validate that the design will meet performance specifications before committing to costly fabrication and assembly.

The Critical Role of Manufacturing and Testing

The most meticulously simulated design can fail if manufacturing tolerances are not accounted for and controlled. Close collaboration with the PCB fabricator is essential. Designers must provide clear impedance control drawings specifying target values, tolerance (typically ±10%), the relevant layers, and trace geometries. Fabricators use controlled impedance test coupons—small test structures placed on the panel edge—to measure the produced impedance using a TDR instrument. These coupons must accurately represent the actual board's stack-up and trace construction.

Post-manufacturing, testing of the assembled board may also be required. Vector network analyzer (VNA) measurements can characterize the scattering parameters (S-parameters) of critical channels, quantifying insertion loss and return loss (a measure of reflections) across the operational frequency band. This real-world data validates the design and manufacturing process, closing the loop on impedance control. For the most demanding applications, this rigorous approach to design, material selection, simulation, and verification is not optional; it is the essential methodology for conquering the challenges of high-frequency PCB design and ensuring signal integrity from DC to daylight.

REPORT