-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

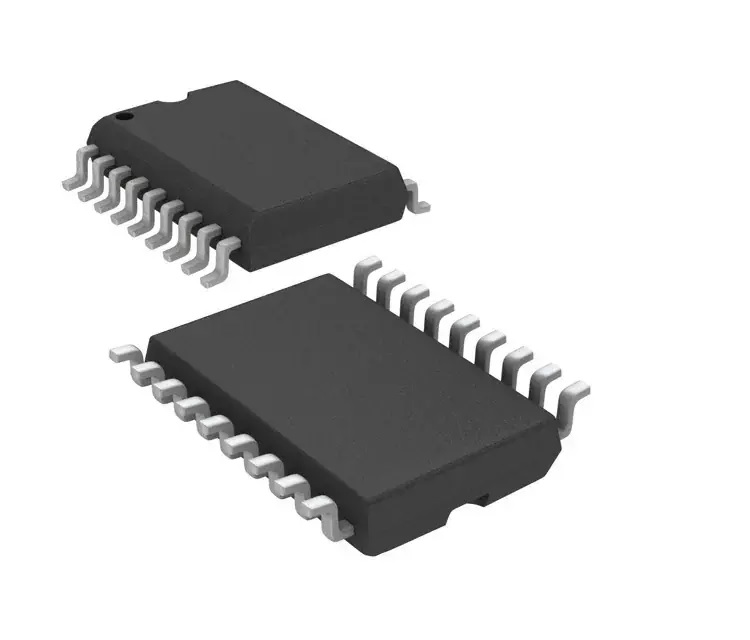

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

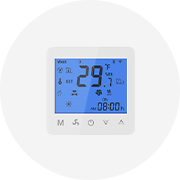

- Floor Heating Systems & Parts

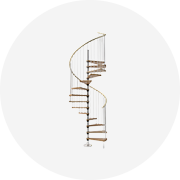

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

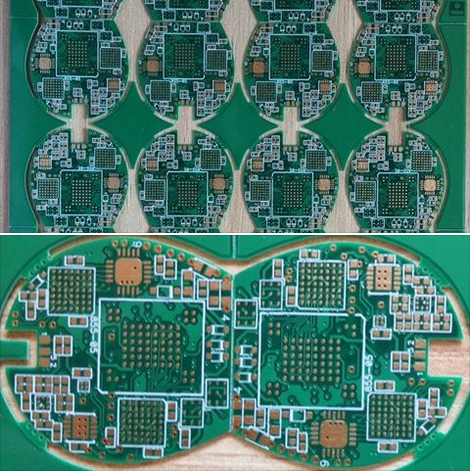

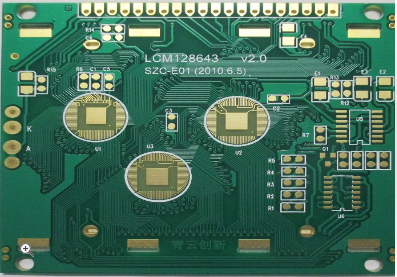

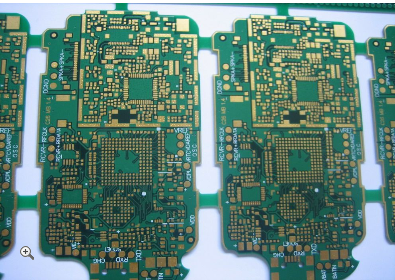

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

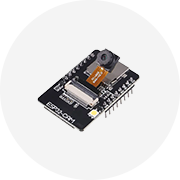

Optimizing Component Placement And Routing In Modern PCB Layout Design

In the rapidly evolving landscape of electronics, the printed circuit board (PCB) remains the fundamental backbone, interconnecting components to bring a design to life. However, as devices become more powerful, compact, and complex, the task of laying out these boards has transformed from a simple connective exercise into a critical engineering discipline. Optimizing component placement and routing in modern PCB layout design is no longer a mere step in the process; it is the decisive factor between a high-performance, reliable product and one plagued by signal integrity issues, thermal problems, and manufacturing failures. This intricate dance of positioning components and tracing copper pathways directly influences electrical performance, electromagnetic compatibility (EMC), thermal management, manufacturability, and ultimately, the cost and time-to-market. For engineers and designers, mastering this optimization is the key to unlocking the full potential of today's advanced integrated circuits and high-speed interfaces, making it a compelling and essential field of study.

The Foundational Strategy: Intelligent Component Placement

The journey of optimization begins long before the first trace is drawn, with the strategic placement of every component on the board. This phase sets the stage for all subsequent routing and profoundly impacts the board's functionality. Effective placement starts with a logical grouping of components based on their functional blocks, such as power supply, microcontroller, memory, and RF sections. Keeping related components close together minimizes the overall trace lengths for critical signals, reducing parasitic inductance and capacitance that can degrade performance.

Beyond functional grouping, placement must account for mechanical and thermal constraints. Connectors, switches, and displays often have fixed locations dictated by the product enclosure. Large, heat-generating components like processors or power regulators must be positioned to facilitate heat dissipation, possibly near the board edge or directly under a heatsink. Furthermore, considering the assembly process is crucial. Placing components to enable efficient automated pick-and-place machine paths and ensuring adequate spacing for soldering and inspection tools can drastically reduce manufacturing defects and costs. A well-considered placement is a balanced compromise between electrical performance, physical constraints, and production practicality.

Navigating Electrical Performance: Signal and Power Integrity Routing

Once components are strategically placed, the focus shifts to the art and science of routing the copper traces that carry signals and power. For modern high-speed digital circuits and sensitive analog sections, routing is paramount for signal integrity. Critical signals, such as clock lines and differential pairs (e.g., USB, PCIe), require controlled impedance routing. This involves calculating and maintaining a specific trace width and spacing relative to the reference ground plane to achieve a target impedance, preventing signal reflections and ensuring clean data transmission.

Power integrity is equally vital. The power distribution network (PDN) must deliver stable, low-noise voltage to all components. This is achieved by using dedicated, wide power and ground planes within the PCB stack-up to provide low-impedance paths. For high-current paths, traces must be sufficiently wide to avoid excessive heating. Careful decoupling is also part of routing strategy; placing small bypass capacitors as close as possible to the power pins of ICs provides a local charge reservoir, suppressing high-frequency noise on the power rails. Proper routing for signal and power integrity ensures the electronic system operates reliably at its intended speed and power.

Ensuring Reliability: Thermal Management and EMC Considerations

A PCB that functions electrically but overheats or interferes with itself (or other devices) is a failure. Optimization must therefore integrate thermal management and electromagnetic compatibility (EMC) from the ground up. Thermally, routing can help by using thicker copper or dedicated copper pours (fills) on outer layers to act as heat spreaders, drawing heat away from hot components. Strategic placement of thermal vias—an array of plated holes—under a component's thermal pad can conduct heat efficiently to inner ground planes or a dedicated back-side heatsink.

For EMC, the goal is to minimize both the emission of and susceptibility to electromagnetic interference. A fundamental practice is maintaining a continuous, unbroken ground plane, which provides a shield and a return path for signals. High-speed traces should be routed over this solid ground plane, and sensitive traces must be kept away from noise sources like switching power supplies or clock generators. For particularly noisy sections, guard traces—grounded traces running parallel to a sensitive line—or even full shielding cans may be necessary. By proactively designing for thermal and EMC performance during placement and routing, designers prevent costly board spins and compliance testing failures later.

Leveraging Modern Tools and Design for Manufacturing

The complexity of modern PCB optimization is untenable without sophisticated electronic design automation (EDA) software. These tools are indispensable partners, offering features like real-time design rule checking (DRC), which enforces constraints for trace width, spacing, and layer usage. Auto-routers have evolved, but their most effective use is often for completing non-critical connections after the designer has manually routed the critical, high-speed paths. More advanced tools provide simulation capabilities for signal integrity, power integrity, and thermal analysis, allowing designers to virtual prototype and refine their layout before fabrication.

Finally, all optimization must be validated through the lens of Design for Manufacturing (DFM) and Design for Assembly (DFA). This means adhering to the fabricator's capabilities regarding minimum trace/space, hole sizes, and copper-to-edge clearance. It involves creating clear solder mask layers to prevent bridging and providing a comprehensive silkscreen for assembly identification. A design that is electrically perfect but cannot be reliably built is not optimized. The ultimate goal is a layout that achieves peak performance while being robust, cost-effective, and straightforward to manufacture at scale, seamlessly bridging the gap between digital design and physical reality.

REPORT